A 0.36 pJ/bit, 12.5 Gb/s forwarded-clock receiver with a sample swapping scheme and a half-bit delay line | Semantic Scholar

Secrecy rate versus the number of key bits per jamming symbol (k) for... | Download Scientific Diagram

Figure 3 from A 0.9 pJ/bit, 12.8 GByte/s WideIO memory interface in a 3D-IC NoC-based MPSoC | Semantic Scholar

Energy consumption per access and bit error rate for an SRAM built on a... | Download Scientific Diagram

Table II from A 1.4 pJ/bit, Power-Scalable 16×12 Gb/s Source-Synchronous I/O With DFE Receiver in 32 nm SOI CMOS Technology | Semantic Scholar

Total energy per bit processed against number of operations per bit.... | Download Scientific Diagram

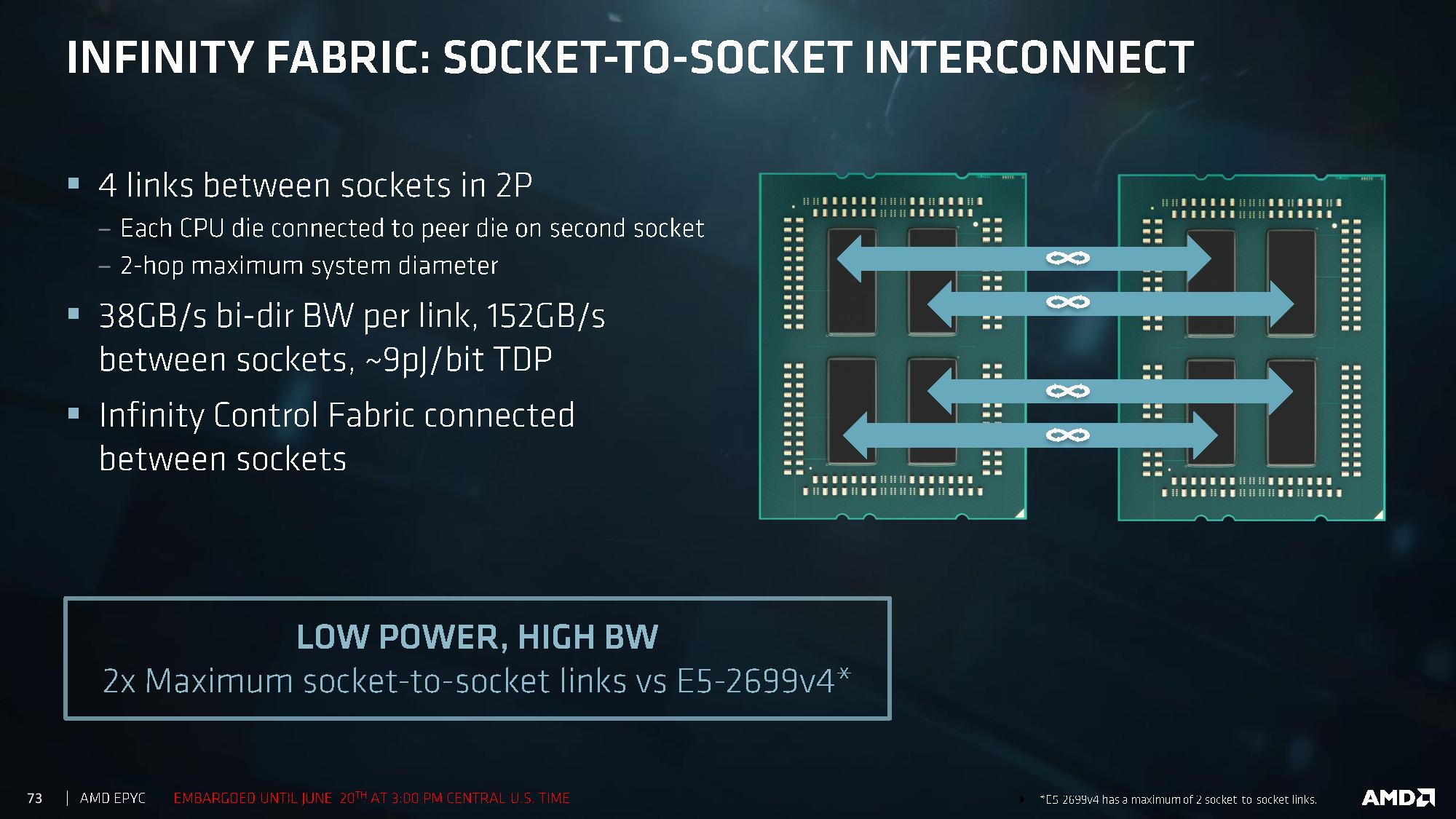

NUMA NUMA: Infinity Fabric Bandwidths - AMD's Future in Servers: New 7000-Series CPUs Launched and EPYC Analysis

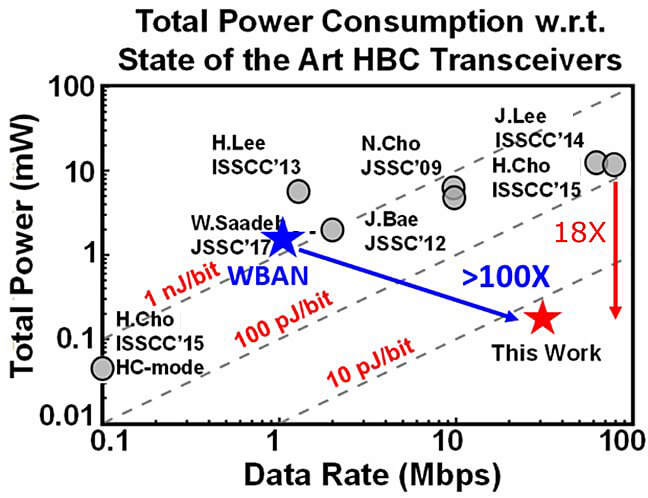

Global honor recognizes Purdue innovator for using the human body as a wire to improve health care, neuroscience - Purdue University News

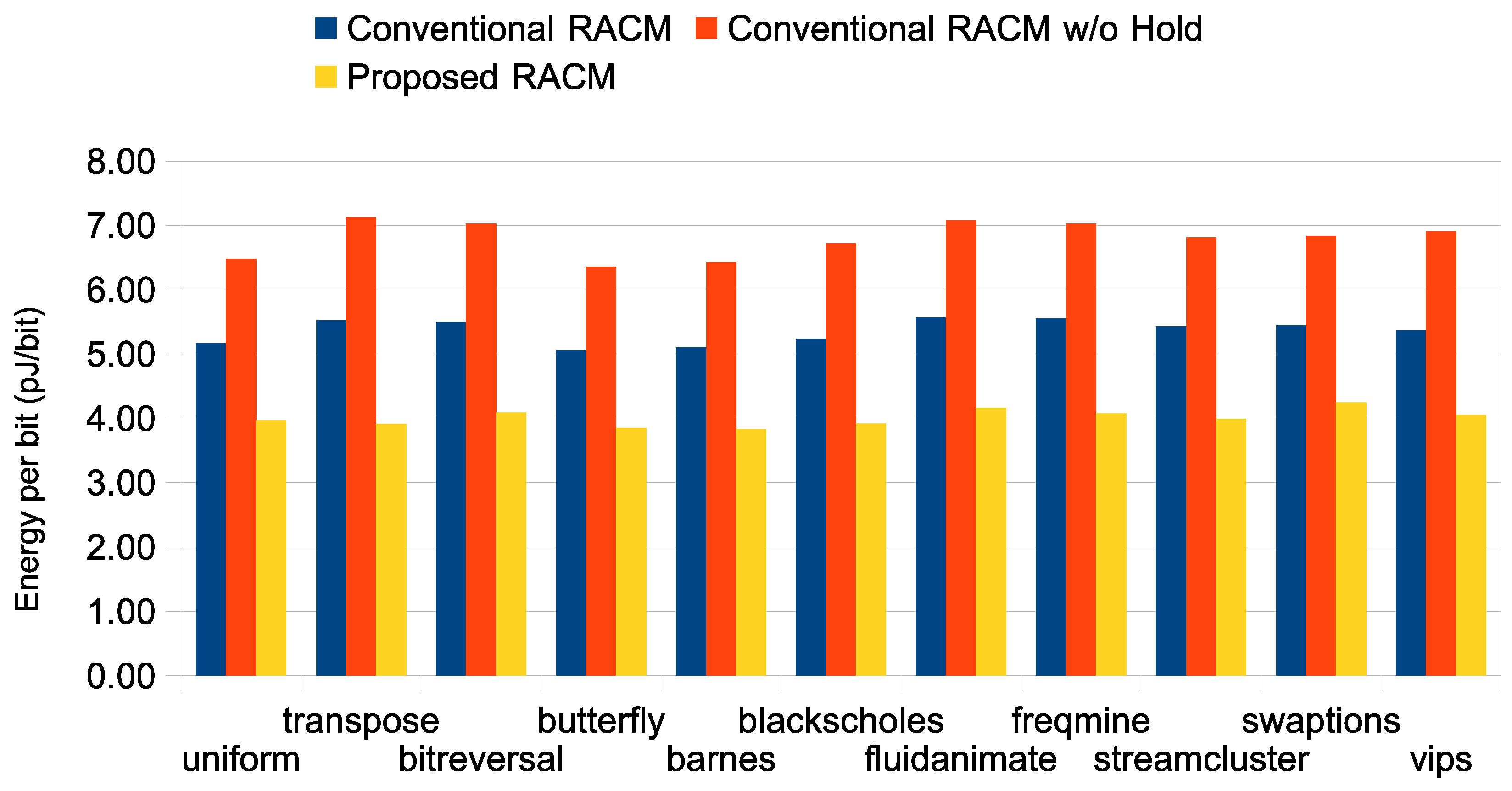

JLPEA | Free Full-Text | An Efficient Radio Access Control Mechanism for Wireless Network-On-Chip Architectures | HTML