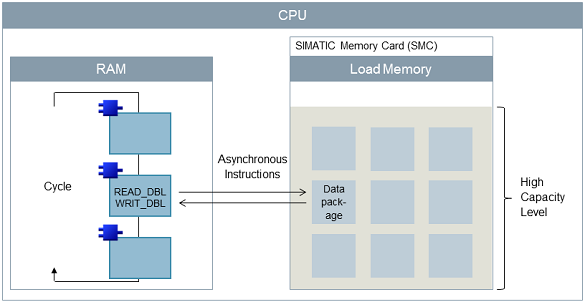

With the CPU S7-1500, why can the length of the cycle time be dependent on the me... - ID: 109749098 - Industry Support Siemens

What Are Memory Timings? CAS Latency, tRCD, tRP, & tRAS (Pt 1) | GamersNexus - Gaming PC Builds & Hardware Benchmarks