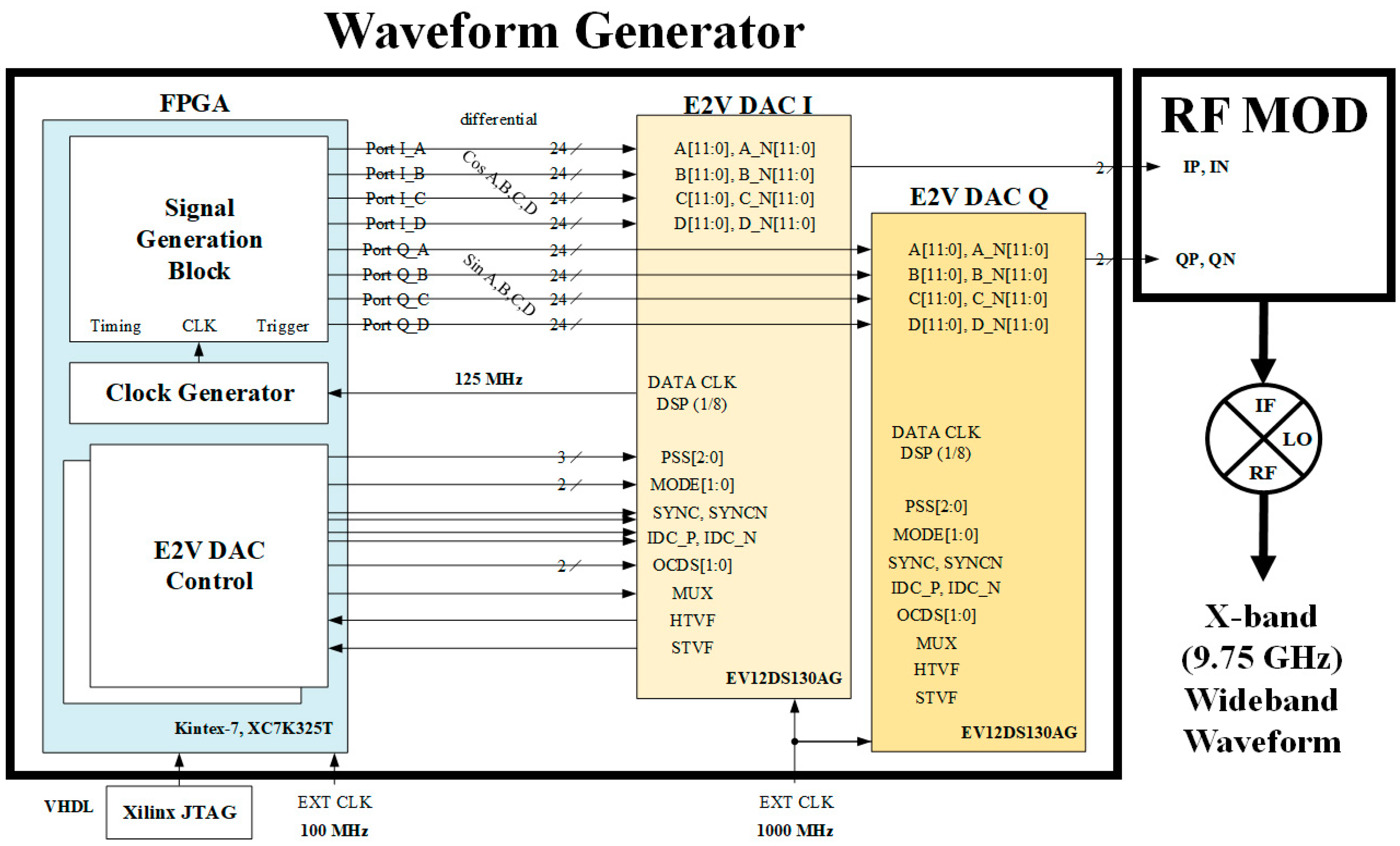

Remote Sensing | Free Full-Text | Wideband Waveform Generation Using MDDS and Phase Compensation for X-Band SAR | HTML

xilinx - System Generator: How to configure the CORDIC divider block. Understanding the block parameters - Electrical Engineering Stack Exchange